## Der MOS Transistor mehr quantitativ

Advanced

## **Some Quantitative Considerations**

the gate electrode from the same kind of **n-Si** as the substrate, just highly doped so it is as metallic as possible - we have the same kind of band diagram then to the left and right of the gate dielectric

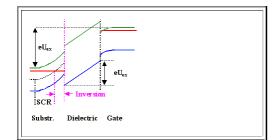

## The decisive part is achieving inversion. Lets see how that looks like in a band diagram. To make life easier, we make Lets look schematically what that will give us for some basic cases: Voltage at the gate **Conditions in the Si** Voltage drop Charge distribution Zero gate voltage. "Flat band" condition Nothing happens. The We only would have There are no net band in the substrate a voltage (or better charges is perfectly flat (and so potential) drop, if the is the band in the Fermi energies of contact electrode, but substrate and gate that is of no interest). electrode were different . Dielectric Substr. Gate Pos. gate voltage. Accumulation The voltage drops There is some pos. With a positive voltage at the gate we attract mostly in the oxide charge at the gate the electrons in the electrode interface eUex (with our Si electrode substrate. The bands must bend down from the SCR), and somewhat, and we negative charge from ∎eU., the many electrons in increase the number of Dielectric Gate Substr electrons in the the (thin) accumulation conduction band layer on the other side accordingly. (There is a of the gate dielectric. bit of a space charge region (SCR) in the contact, but that is of no interest). Small neg. gate voltage. Depletion With a (small) negative The voltage drops There is some negative voltage at the gate, we mostly in the oxide, charge at the gate repel the electrons in but also to some electrode interface the substrate. Their extent in the SCR. (accumulated electrons eU.. with our Si electrode), concentration decreases, the hole and positive charge SCR smeared out in the the concentration is still Dielectric Gate Substr. low - we have a layer (extended) SCR layer on the other side of the depleted of mobile carriers and therefore a gate dielectric. SCR. Large neg. gate voltage. Inversion

With a (large) negative voltage at the gate, we repel the electrons in the substrate very much. The bands bend so much, that the Fermi energy (red line) is in the lower half of the band close to the interface. In this region holes are the majority carriers, we have *inversion*. We still have a **SCR**, too.

The voltage drops mostly in the oxide, but also to some extent in the SCR and the inversion layer. There is more *negative charge* at the gate electrode interface (accumulated electrons with our **Si** electrode), some *positive charge* smeared out in the the (extended) **SCR** layer on the other side of the gate dielectric, and a lot of *positive charge* from the holes in thin inversion layer.

Qualitatively, this is clear. What happens if we replace the (highly **n**-doped) **Si** of the gate electrode with some metal (or **p**-doped **Si**)?

Then we have different Fermi energies to the left and right of the contact, leading to a built-in potential as in a pnjunction. We will than have some band bending at zero external voltage, flat band conditions for a non-zero external voltage, and concomitant adjustments in the charges on both sides.

But while this complicates the situation, as do unavoidable fixed immobile charges in the dielectric or in the Sidielectric interface, nothing new is added.

Now, the decisive part is achieving inversion. It is clear that this needs some minimum threshold voltage **U**<sub>th</sub>, and from the pictures above, it is also clear that this request translates into a request for some *minimum charge* on the capacitor formed by the gate electrode, the dielectric and the **Si** substrate.

What determines the amount of charge we have in this system? Well, since the whole assembly for any distribution of the charge can always be treated as a simple capacitor C<sub>G</sub>, we have for the charge of this capacitor, .

Since we want *U*th to be small, we want a *large gate capacitance* for a large charge *Q*<sub>G</sub>, and now we must ask: What determines *C*<sub>G</sub>?

If all charges would be concentrated right at the interfaces, the capacitance *per area unit* would be given simply by the geometry of the resultant plate capacitor to

With dox = thickness of the gate dielectric, (so far) always silicon dioxide SiO2.

Since our charges are somewhat spread out in the substrate (we may neglect this in the gate electrode if we use metals or very highly doped **Si**), we must take this into account.

In electrical terms, we simply have a second capacitor **C**<sub>Si</sub> describing the effects of spread charges in the Si, switched in series to the geometric capacitor which we now call **oxide** capacitance **C**<sub>Ox</sub>. It will be rather large for concentrated charges, i.e. for accumulation and inversion and small for depletion.

The total capacitance **C**G then is given by

For inversion and accumulation, when the most of the charge is close to the interface, the total capacitance will be dominated by **C**<sub>0x</sub>. It is relatively large, because the thickness of the capacitor is small.

In the depletion range, **C<sub>Si</sub>** will be largest and the total capacitance reaches a minimum.

In total,  $C_G$  as a function of the voltage, i.e.  $C_G(U)$  runs from a constant value at large positive voltages through a minimum back to about the same constant value at large positive voltages. The resulting curve contains all relevant information about the system. Measuring  $C_G(U)$  is thus the first thing you do when working with **MOS** contacts.

While it is not extremely easy to calculate the capacitance values and everything else that goes with it, it can be <u>done</u> - just solve the <u>Poisson equation</u> for the problem.

All things considered, we want **C**<sub>Ox</sub> to be *large*, and that means we want the dielectric to be *thin* and to have a *large* dielectric constant - as <u>stated above</u> without justification.

We also want the dielectric to have a large <u>breakdown field strength</u>, no fixed charges in the volume, no interface charges, a very small tg δ; it also should be very stable, compatible with **Si** technology, and cheap.

In other words, we wantedSiO<sub>2</sub> - even so its dielectric constant is just a mediocre 3.9 - for all those years of microelectronic wonders. But now (2001), we want something better with respect to dielectric constants. Much work is done, investigating, e.g., CeO<sub>2</sub>, Gd<sub>2</sub>O<sub>3</sub>, ZrO<sub>2</sub>, Y<sub>2</sub>O<sub>3</sub>, BaTiO<sub>3</sub>, BaO/SrO, and so on. And nobody knows today (2002) which material will make the race!

In **2007** we know more: It's **HfO<sub>2</sub>**; at least for Intel. For reasons of it's own, Intel talks about Hafnium "metal", which makes no sense whatsoever